-

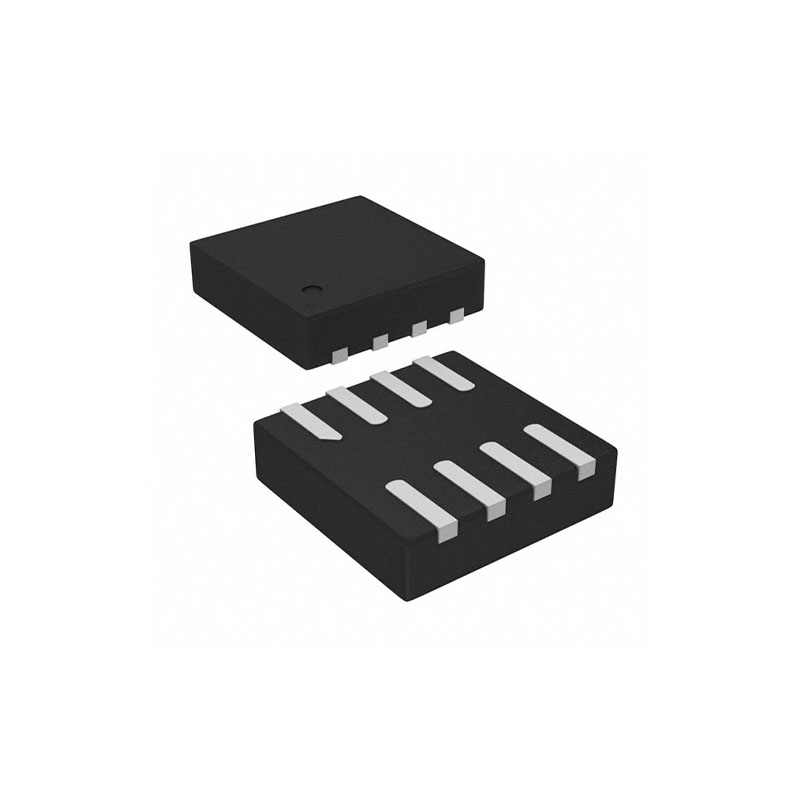

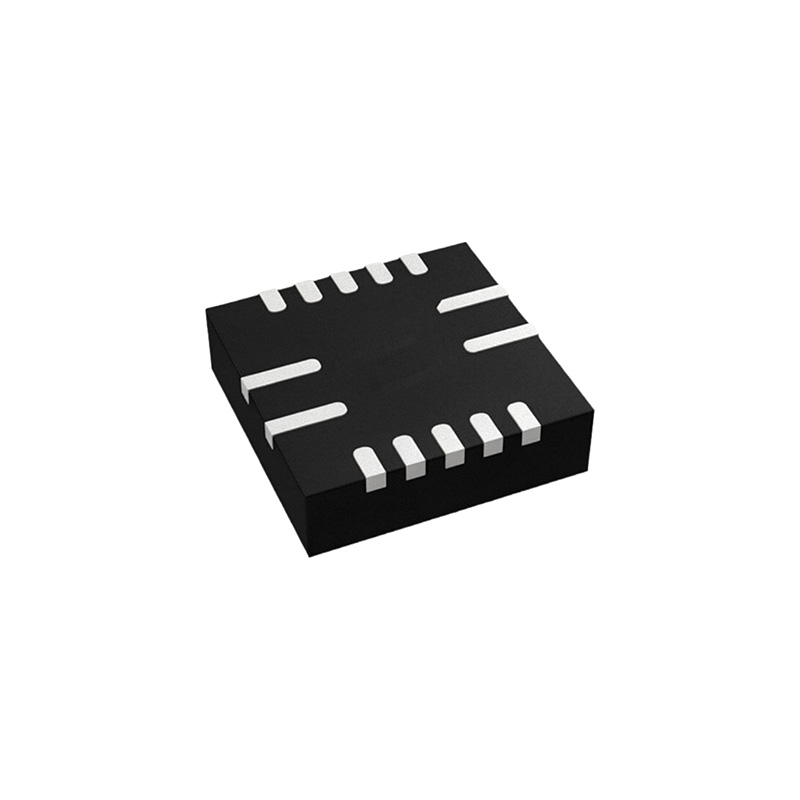

GDQ2BFAA-CQ GD(兆易创新) DDR4 SDRAM(同步动态随机存储器)

电源:VDD = VDDQ = 1.2V (1.14V 至 1.6V);VPP = 2.5V (2.375V 至 2.75V)JEDEC 标准封装:x16 96 FBGA 阵列配置:8 银行 (x16) 2 组 4 银行 8n 位预取架构,突发长度 (B):8 和 4(带突发截断 BC),可编程 CAS 延迟 (CL),可编程 CAS 写延迟 (CWL) 内部生成的数据输入 Vref,片终结 (ODT):支持标称、停机和动态 ODT 差分时钟和数据选通输入 (CK_t,CK_c; DQS_t,DQS_c)

全国服务热线:15361844591

芯片介绍

芯片介绍 Product Introduction

Product Introduction

1、芯片介绍

电源:VDD = VDDQ = 1.2V (1.14V 至 1.6V);VPP = 2.5V (2.375V 至 2.75V)JEDEC 标准封装:x16 96 FBGA

阵列配置:8 银行 (x16) 2 组 4 银行

8n 位预取架构

突发长度 (B):8 和 4(带突发截断 BC)

可编程 CAS 延迟 (CL)

可编程 CAS 写延迟 (CWL)

内部生成的数据输入 Vref

片终结 (ODT):支持标称、停机和动态 ODT

差分时钟和数据选通输入 (CK_t,CK_c; DQS_t,DQS_c)

接口:1.2V 伪开漏 (POD) 10

每 DRAM 可寻址性 (PDA)

数据总线反转DBI)

写数据掩码 (DM)

最大功耗节省模式 (MPSM)

上电异步复位

预充电:每个突发访问的自动充电选项

工作壳温:-40°C ≤ TCase ≤ 95°C

支持自动刷新和自刷新模式

平均刷新周期:

-7.8us 在 -°C ≤ TCase ≤ 85°C

-3.9us 在 85°C < TCase ≤ 95°C

细粒刷新 2x、4x 模式以减小 tRFC

可编程数据选通前导码

支持命令地址 (CA) 奇偶校验

支持写循环冗验 (CRC)

支持连接性测试模式 (TEN)

降速模式

通过 ZQ 引脚进行输出驱动器校准 (RZQ:40 欧姆 ± 1%)

符合 JEDEC JESD-79-4 标准

封装信息

封装信息 Encapsulation information

Encapsulation information

|

产品品牌: |

GD/兆易创新 |

产品描述: |

所有产品均来自正规渠道

支持第三方检测

|

|

产品名称: |

|

产品封装: |

FBGA-96 |

|

标准包装: |

1870个/托盘 |

最低起订: |

1片起售 |

|

出厂日期: |

请咨询客服 |

大货周期: |

现货库存 |

产品应用

产品应用 Product application

Product application

-

通信设备

-

消费电子

-

工业控制

-

智能安防

合作客户

合作客户 Customer

Customer

芯火优势

芯火优势 Advantage

Advantage

-

原厂代理直供,一手货源

代理直供覆盖300+全球知名元器件品牌,一手货源省去中间商环节,让利给终端用户

-

响应速度快,交付保障

10余年服务终端客户经验沉淀,为满足客户紧急生产需求芯火做到1分钟快速响,3分钟精确货源匹配,5分钟报价

-

支持第三方检测,品质保证

时时刻刻关注产品质量,渠道上只有原厂和代理,可追溯原厂品质,支持第三方检测,从原料、性能、外观等方面严格检测从开发到批量生产,确保每一个产品的稳定性;

-

提供技术支持,按需定制

经验丰富的工程师,专注不同行业芯片技术的更新,免费提供技术支持,根据产品应用,深度分析产品需求,进行个性化功能定制

芯火团队

芯火团队 Core Fire Team

Core Fire Team

-

公司团队

-

团队协作

-

公司团队

-

团队协作

芯火资质

芯火资质 honor

honor

-

诚信供应商单位

-

行业诚信单位

-

质量、服务诚信单位

-

重服务守信用单位

采购:GDQ2BFAA-CQ GD(兆易创新) DDR4 SDRAM(同步动态随机存储器)

- *联系人:

- *手机:

- 公司名称:

- 邮箱:

- *采购意向:

-

*验证码:

跟此产品相关的产品 / Related Products

- MP9943GQ-Z MPS(芯源) 高频、同步整流、降压开关转换器

- MP9943是一款高频、同步整流、降压开关转换器,内置功率MOSFET。它提供了一种非常紧凑的案,可在宽输入电压范围内实现3A峰值输出电流,并具有出色的负载和线路调整率。MP9943在输出电流负载范围内采用同步模式工以提高效率。电流模式工作可提供快速的瞬态响应,并简化环路稳定。完整的保护功能包括过流保护和过热关断。MP99所需的外部标准元器件数量极少,且采用节省空间的QFN-8(3mmx3mm)封装。

- MP8859GQ-0000-Z MPS(芯源) 高频同步整流降压开关转换器

- MP8759是一款高度集成的高频同步整流降压开关转换器。它提供了一种非常紧凑的解决方案,在宽入电压范围内可实现8A的连续输出电流和10A的峰值输出电流,并具有出色的负载和线路调整率。基于MPS专有的开关损耗降低技内部低RDS(ON)功率MOSFET,MP8759在宽输出电流负载范围内实现了高效率。自适应恒定导通时间(COT控制模式提供了快速的瞬态响应,并简化了环路稳定。DC自动调谐环路提供了良好的负载和线路调整率。完整的保护功能包括过流制、过压保护(OVP)、欠压保护(UVP)和过热关断。该转换器所需的外部元件最少,采用QFN12

- MP8765GQ-Z MPS(芯源) 高度集成的高频同步整流降压开关模式转换器

- MP8765是一款高度集成的高频同步整流降压开关模式转换器。它在宽输入电压范围内提供非常紧解决方案,可实现6A连续输出电流,并具有出色的负载和线路调整率。MP8765在宽输出电流负载范围内具有高效率。恒通时间(COT)控制模式可提供快速的瞬态响应,并简化环路稳定。欠压锁定(UVLO)内部设置为4.6V。开漏源正常信号指示输出处于其标称电压范围内。全面的保护功能包括过流保护(OCP)和过热关断。该转换器所需的外部件最少,采用QFN16(3mmx3mm)封装。

全国服务热线

全国服务热线

top

top